SLIM-PDM rev C

Phase Detector Module

Phase Detector Module

Updated 10-21-08: Update to reflect SLIM-PDM Revision B

Updated 2-9-09: Update to add Schematic Error Note

Updated 8-11-09: Update to explain voltage source option. Add revision history.

Updated 11-20-10: Update to reflect SLIM-PDM Revision C, addition of 2 capacitors.

Updated 11-25-11: Add links to Archived documents

Updated 5-16-15: Change capacitors. Change Parts List to Rev D and move to this page.

Updated 1-20-16: Update to reflect new printed wiring board, PWB-PDM Rev C. (note: there was no Rev B)

SLIM-PDM, Phase Detector Module, size-A

Use your mouse's "right click" and "Save Link" to download:

a. SKSLIM-PDM rev C, Schematic, in ExpressPCB software.

b. LAYSLIM-PDM rev C, Parts Layout. For parts locations.

c. PLSLIM-PDM Rev D. Parts List. Maintained on this page, only.

d. PWB-PDM rev C, PWB Artwork, in ExpressPCB software. Use to order from Express.

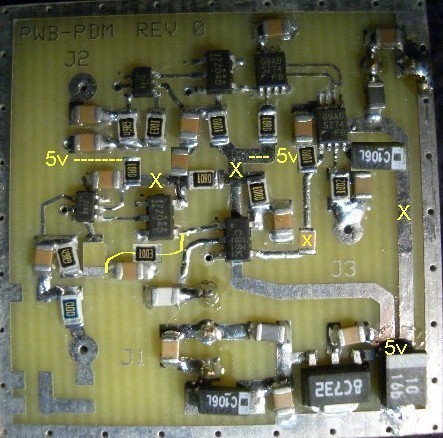

This SLIM-PDM is constructed on a common printed wiring board, the PWB-PDM (rev C). Previously, there was a separate web page for the PWB. I have deleted that page and combined the information on this page. If you have constructed the SLIM-PDM rev A, using the PWB-PDM (rev 0) board, and would like to improve the PDM accuracy, see the Modification Procedure on the end of this page.

The SLIM-PDM is a 360 degree, Phase to Voltage Converter. It is specifically designed to operate at 10.7 MHz, but will operate in the KHz range up to 30 MHz. The J1 and J2 inputs can be sine or square wave . The min / max sine input is -20 dBm to +18 dBm. The min / max square input is 10 mvpp to 5vpp. Input impedance is nominally 50 ohms, but can be changed to any input impedance.

The output, at J3, is a DC voltage that is proportional to the differential phase of the input signals at J1 and J2. The 0v to +5v output should be loaded with 100 K or higher. A realistic measurable phase range is from 20 degrees to 340 degrees with error less than .1 degrees.

Power requirements for the SLIM-PDM is +7 volts to +15 volts at 50 ma.

Option when using PDM in MSA/VNA

The PDM has a provision to source +5 volts to a separate Analog to Digital Converter module, the SLIM-ADC. This allows both modules to use the same regulated +5volts. This allows for more accurate Phase measurements. The SLIM-PDM Rev 0 requires no change or modification for this application. Later revisions require the placement of FBx.

Engineering Change Notice, ECN-11-20-2010

Although rare, the PDM rev B may have a tendency to "self oscillate". A modification is made to prevent this rare instability. If your PDM rev B is operating normally you may omit the modification. To modify and update SLIM-PDM-revB into SLIM-PDM-revC, the addition of two capacitors is necessary (C24 and C25). See schematic, SKSLIM-PDM Rev C. Also see LAYSLIM-PDM-Rev C.

When building a new SLIM-PDM rev C using the PWB-PDM Rev A, the capacitors do not have pwb pads and should be placed according to the layout (see below). Adding the jumper wire to U9-6 (or U9-3) is difficult since the IC is so small. I would suggest the PDM be built and tested in its final configuration before this modification is performed. It may not even be necessary.

This ECN is incorporated on the PWB-PDM Rev C. (see below)

Layout and parts locator for SLIM-PDM

Updated 1-20-16: The document "layslim_pdm.gif" is used to locate parts on the board. To order PWB from Express, use pwb-pdm.pcb

Note: The layout and schematic show that there are two ferrite beads supplying U5, FBx and FB2. The installation of these beads is determined by how the SLIM-PDM is used in a final configuration of a high level system.

SKSLIM-PDM, Schematic of SLIM-PDM